Micro-LEDs:表面复合和光提取的建模

Micro-LEDs:表面复合和光提取的建模

★表面复合模型

★圆形μ-LED中表面复合的影响

★微反射镜下方形台面截断金字塔LED的研究

Micro-LEDs:表面复合和光提取的建模

- Surface recombination model

- Effect of surface recombination in circular μ-LEDs

- Study of square-mesa truncated pyramid LED with micro reflector

模拟软件的功能最近已经扩展到包括专门用于模拟微型器件的功能。现在,它们包括通常与 LED 尺寸向 μ-LED 缩小相关的几种主要效应的模型:电流拥挤、LED 自热增加、表面复合导致的载流子损失、与小型化相关的光提取效应。在本页中,我们给出了这些新选项的简要说明。欢迎您联系我们了解更多详情。

1.表面复合模型

在模拟仿真 SimuLED 软件的 SpeCLED 模块中可以对 LED 芯片中的表面复合进行模拟。然而为了模拟表面复合,首先应该建立有源区中的 p-n 结偏压、电流密度、IQE、发射波长、注入系数和载流子浓度之间的关系。这些计算是在 SiLENSe 软件进行的,在那里确定了异质结构的有源区。然后使用这些数据在 SpeCLED 软件的芯片级上模拟 LED 台面侧壁处的表面复合效应的影响。即该软件将有源区中的横向载流子传输作为对 3D 电流扩展解的校正。请注意,这种校正并不意味着注入有源区的总垂直电流的任何变化,而仅仅只是它在复合和横向扩散之间的重新分布,以适应有源区周边的表面复合速度。

Schematic view of a circularly-shaped LED dice used for self-consistent electrical / thermal / optical simulations

2.圆形 μ-LED 中表面复合的影响

当 micro-LEDs 在高电流密度下工作时,由于俄歇复合使它们容易损耗。与较大的同类产品不同,较小的特征尺寸也增加了有源区周边表面重组的影响。因此,要成功缩小LED尺寸需要准确考虑影响发射效率的几种机制的相互作用。例如,表面复合造成的载流子损耗不仅取决于LED芯片的绝对横向尺寸,还取决于电流拥挤情况。然而,后者导致了在强电流局部化区域中较高的局部效率下降。同时,影响表面复合和电流拥挤的有源区域中双极性扩散的长度本身也取决于非平衡载流子密度,或者换句话说,取决于电流密度。因此,提高 micro-LEDs 的效率需要对器件结构、芯片设计及其工作条件进行耦合优化。

Above: Current crowding and surface recombination in a circular micro LED at different chip sizes and current densities

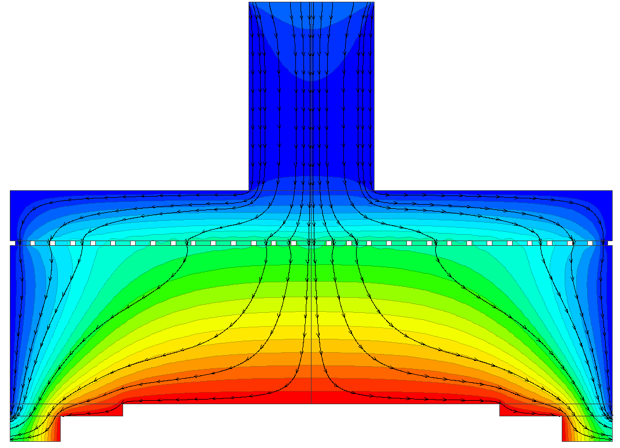

我们考虑了一个圆形的 LED 芯片作为一个简单的例子,见下边的图像。为了进行全芯片建模,首先在 SiLENSe 软件中计算了一个局部偏差和温度范围内的有源区域的特征。这些结果被用于 LED 芯片内/外的电流扩散、加热和光提取的自洽建模。复合电流密度作为径向位置的函数说明了电流拥挤和表面复合的相互作用。下图数值模拟的详细摘要见 (*)。该出版物中研究的扩展趋势包括电流密度-电压特性的演变、光提取和发射效率、电效率和器件的自加热的演变。

Recombination current density as a function of radial position in a 300 μm chip.

Recombination current density as a function of radial position in a 30 μm chip.

3.带有微反射器的截断金字塔形LED

我们接下来要考虑的 μ-LED 芯片是一个正方形截顶金字塔。其示意图如下图所示。我们可以看到由二氧化硅(SiO2)制成的绝缘层将 μ-LED 芯片与高反射金属 n 触点隔开。这层薄薄的二氧化硅对有源区发出的光的反射有显著影响(详见 **)。

我们研究了被二氧化硅薄膜覆盖的块状 Ag(n 型电极的常用材料)上入射光子的反射情况。我们计算了几种厚度的二氧化硅薄膜对波长为 453 纳米的光子的入射角反射系数。计算针对入射光的两种偏振:横向电(TE)和横向磁(TM)。在二氧化硅厚度较小时(dSiO2 = 50 nm),TE 偏振光的反射率在整个角度变化范围内均高于 90%。然而,当角度接近银的布儒斯特角时,TM 偏振光的反射率会出现明显下降,见右图。由于发射出的光子在 μ-LED 内部传播,并在一次反射和另一次反射之间改变其入射角和偏振,这种倾斜会导致不完全反射引起的光学损耗,并最终导致较低的 LEE。

当二氧化硅薄膜的厚度增加时,这种凹陷的幅度大大减小,但 TE 偏振光的反射率却略有降低。这种转变导致二氧化硅层较厚的 μ-LED 晶粒具有较高的锂电效应。然而,绝缘体厚度增加到 250 nm 以上时,LEE 并没有进一步提高。因此,250 nm 的二氧化硅薄膜厚度被认为是最佳厚度,并将在下面的模拟中使用。

接下来,我们考虑了底半球的反射率与由斜面形成的微反射器的形状和大小的关系。

Schematic view of the μ-LED shaped as square truncated pyramid

Reflection coefficients for the photons with the wavelength of 453 nm versus their incident angle for different thicknesses of SiO2 film

计算结果(包括下面显示的所有三幅图)有两个明显的李氏最大值,中间有一个最小值。我们对这些结果的解释如最右边的示意图所示。第一个最大值对应的是光线很快离开芯片,而第二个最大值则代表光线在经过大量内部反射后被提取出来,因为强烈倾斜的台面在很大程度上将发射的光线引向了底面的法线方向。在 35 和 45 度角之间观察到的 LEE 最小值对应于不利的刻面倾斜度,由于 LED 芯片内部的光捕获,会产生较高的光学损耗。有关不同光学损耗机制、其性质和相对贡献的详细讨论,请参见 (**)。

Light extraction efficiency to the bottom hemisphere for different inclination angles of the mesa facet

Publications

“Enhanced microLED efficiency via strategic pGaN contact geometries” by Keith Behrman1 and Ioannis Kymissis1,2; 1 – Electrical Engineering Department, Columbia University, New York City, NY 10027, USA; 2 – Lumiode, The Bronx, NY 10451, USA; Optics Express Vol. 29, Issue 10, pp. 14841-14852 (2021)

(**) “Effect of Die Shape and Size on Performance of III-Nitride Micro-LEDs: A Modeling Study“ by Kirill A. Bulashevich, Sergey S. Konoplev and Sergey Yu. Karpov, Photonics 2018, 5(4), 41

(*) “From Large‐Size to Micro‐LEDs: Scaling Trends Revealed by Modeling” by Sergey S. Konoplev, Kirill A. Bulashevich, Sergey Yu. Karpov, (2017) https://doi.org/10.1002/pssa.201700508

“Impact of surface recombination on efficiency of III-nitride light-emitting diodes” by Kirill A. Bulashevich and Sergey Yu. Karpov, PSS Rapid Research Letters, Volume 10, Issue 6, June 2016, Pages: 480–484